Connection to DriversCloud Create a DriversCloud.com account Reset your DriversCloud.com password Account migration

Intel sets the release date for its Meteor Lake generation at December 14, 2023

The Meteor Lake generation, which has been talked about repeatedly for almost two years, is finally ready for the market.

In October, Intel will release its 14th generation of desktop processors, the Raptor Lake Refresh. However, Intel is hardly communicating about this new wave. Indeed, for the American company, Raptor Lake Refresh is just an intermediary, an almost stop-gap generation, while Intel is preparing for a small revolution with the release, next, of the Meteor Lake generation. We've known about " next " for some time, but what's been missing is any specific information, a date to mark with a white stone in our diaries.

At the opening of Intel Innovation 2023, Intel's event dedicated to its new technologies, it was the chairman of the American group himself who took the floor. Pat Gelsinger gave an update on Intel's immediate future, confirming that Meteor Lake will indeed be released before the end of the calendar year, and finally revealing that December 14 will be THE date to remember for all processor lovers. The Meteor Lake architecture will therefore be launched in mid-December, and we can only imagine that the independent press will be able to give us a real look at what it has in store.

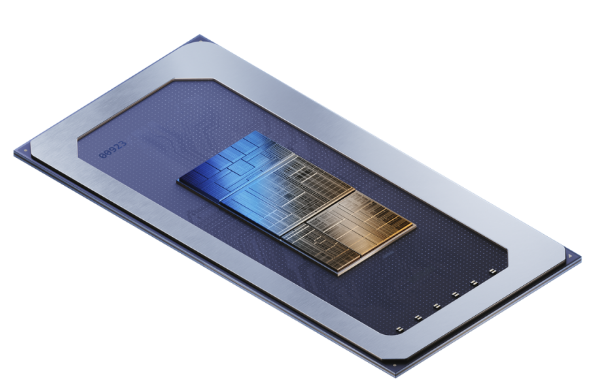

It's worth remembering that Intel is betting heavily on this generation, which is an opportunity to introduce a design relatively close to AMD's chiplets. In fact, Intel seems to be going even further with what it calls " disaggregated design ": the idea is to combine cores of very different origins and technologies on a subtrate that acts as a link, in order to make the chip as complete and versatile as possible. In the case of the first Meteor Lakes, this means combining high-performance cores and efficient cores within the " compute tile ". The Xe-LPG graphics cores will take their place inside the graphic tile, and two other tiles are planned: one to manage I/O and the other to constitute a kind of vital processor center, the SoC tile, which will feature two efficient cores. A date is therefore set.