Connexion à DriversCloud Créer un compte DriversCloud.com Réinitialisation du mot de passe DriversCloud.com Migration du compte

Pour « suivre » la loi de Moore, Intel repense ses transistors

De nouvelles techniques pour l’interconnexion et l’empilement des transistors doivent permettre de pousser toujours plus loin la densité et la précision des processeurs.

Il y a cinquante ans de cela, – en 1971 – Intel commercialisait son premier microprocesseur, le 4004 composé de 2 250 transistors. Le 8086, premier processeur 16-bit de l’Américain, en intégrait pour sa part 29 000 puis nous sommes passés à 275 000 sur le 80386 et même 1 180 235 transistors sur le 80486 avant la révolution Pentium et ses 3 100 000 transistors. Des chiffres impressionnants pour les années 70, 80 et 90, mais qui semblent aujourd’hui bien dérisoires quand Intel avance le nombre de 3 200 000 000 sur les Core i7 Broadwell de 2016. Aujourd’hui, l’Américain ne communique plus ce genre de chiffres, mais continue ses travaux afin d’en « caser toujours ».

À l’occasion de la 67e édition de l’IDEM ou International Electron Devices Meeting, Intel a notamment évoqué plusieurs avancées pour nous présenter ce qu’il envisage pour le futur de ses processeurs. Dans la vidéo ci-dessus, c’est Marko Radosavljevic, ingénieur principal chez Intel, qui entre dans les détail des différentes techniques d’empilement associées à divers substrats utilisés par la société américaine dans le but de multiplier la densité au sein de ses puces. Il est notamment question de 3D CMOS dont l’accroissement de l’empilement de 30 à 50% par rapport aux techniques actuelles doit permettre de regrouper toujours plus de de transistors au millimètre carré.

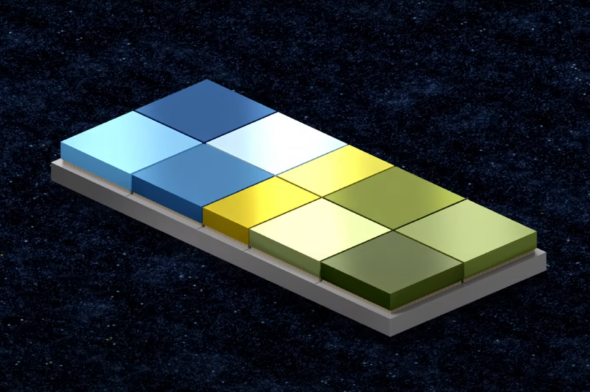

À l’heure actuelle, Intel exploite le processus de gravure Intel 7 sur les processeurs de génération Alder Lake. Par la suite, il envisage le passage à l’Intel 4 et l’Intel 3. Des évolutions qui seront notamment rendues possible par l’utilisation du packaging Foveros Direct en lieu et place de Foveros. L’objectif est ici la multiplication des interconnexions afin, bien sûr, de maximiser les échanges. Intel a déjà parlé de ces améliorations, notamment lors de l’Intel Accelerated de juillet dernier. Foveros Direct exploite des connexions dites « cuivre-à-cuivre » miniaturisées par rapport à Foveros de sorte que sur un espace donné le nombre d’interconnexions est drastiquement plus importants et qui dit plus d’interconnexions, dit davantage d’échange entre les différentes parties des chiplets. Intel souligne d’ailleurs que Foveros Direct autorise également une plus grande modularité de conception. Tout ceci est résumé en trois mots, l’Hybrid Bonding Interconnect, ou HBI.

Enfin, lors de cette 67e édition de l’IDEM, Intel a aussi parler de remplacer les transistors dits FinFET (field-effect transistor ou transistor à effet de champ à ailettes). Comme peuvent aussi l’envisager Samsung ou TSMC, Intel va passer aux GAA FET (gate-all-around) une technique qui vise à modifier la structure du transistor afin que davantage de canaux soient mis en place. Dans ce cas précis, le but est recherché est d’augmenter la précision et, surtout, la stabilité des transistors, un sujet essentiel dès lors que l’on affine encore et toujours le processus de gravure. L’introduction de transistors GAA FET chez Intel ne devrait toutefois pas se faire avant 2024 et l’utilisation du processus Intel 20A..