الاتصال DriversCloud إنشاء حساب في DriversCloud.com إعادة تعيين كلمة السر على DriversCloud.com ترحيل الحساب

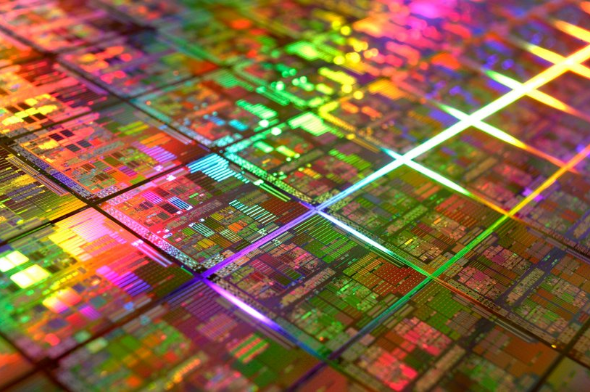

نحو تسمية جديدة لعمليات النقش في إنتل؟

قم بتسمية عقد النقش بشكل مختلف لحساب كثافة الترانزستور بشكل أفضل.

ليس سرا أن أي شخص يتابع أخبار أشباه الموصلات من قريب أو بعيد ، إذا ظلت Intel عملاقا في القطاع ، فهي أيضا في صعوبة كبيرة في بعض العمليات التقنية. لعدة سنوات حتى الآن ، يبدو أن لديها كل المتاعب في العالم لتطوير عملية نقش المكونات نحو 10 نانومتر و 7 نانومتر في حين أن أحد منافسيها الرئيسيين - TSMC التايواني - يتحدث بالفعل عن الانتقال إلى 5 نانومتر أو حتى 4 نانومتر و 3 نانومتر.

في الواقع ، في حين أن AMD - شريك TSMC - تمكنت من تسويق سلسلة Ryzen 5000 الجديدة وفقا لعملية 7 نانومتر ، فقد وزعت Intel للتو نطاق Rocket Lake-S الجديد مع عملية 14 نانومتر: من وجهة نظر تسويقية صارمة ، فهي ليست مباعة للغاية. لذلك تخطط إنتل لإعادة التفكير في الطريقة التي تسمي بها عملية النقش الخاصة بها ولم تعد تعكس الدقة الوحيدة للنقش لتأخذ في الاعتبار أيضا كثافة الترانزستورات لكل ملليمتر مربع. هذه بالتأكيد مناورة تسويقية ، ولكن ليس فقط.

تجدر الإشارة إلى أنه لا يتم إنشاء جميع عمليات النقش على قدم المساواة. لا يوجد "معيار" في هذا المجال لاستحضار هذه العملية أو تلك وبراعتها وجودتها. وبالتالي ، تشير Intel إلى أن 10 نانومتر أكثر كفاءة بكثير من 7 نانومتر في TSMC: 10 نانومتر تسمح للأمريكي بالوصول إلى كثافة ترانزستور تبلغ 100.8 مليون ترانزستور لكل ملليمتر مربع (MT / mm²) عندما يجب أن يكون التايوانيون راضين عن 90 MT / mm² على 7 نانومتر. وفقا ل Oregon Live ، فإن الفكرة تشق طريقها إلى Intel لمراجعة تسميتها بالكامل والدعوة إلى شيء أكثر عالمية.