Ligação a DriversCloud Criar uma conta DriversCloud.com Reiniciar palavra-passe de DriversCloud.com Migração de contas

Intel repensa transistores para 'seguir' a Lei de Moore

Novas técnicas de interconexão e empilhamento de transistores devem permitir empurrar ainda mais a densidade e precisão dos processadores.

Há 50 anos atrás, em 1971, a Intel comercializou seu primeiro microprocessador, o 4004, que consistia em 2.250 transistores. O 8086, o primeiro processador de 16 bits da empresa americana, tinha 29.000 transistores, depois fomos para 275.000 no 80386 e até 1.180.235 transistores no 80486 antes da revolução Pentium e seus 3.100.000 transistores. Estes são números impressionantes para os anos 70, 80 e 90, mas parecem muito insignificantes hoje, quando a Intel apresenta o número de 3.200.000.000 no Core i7 Broadwell de 2016. Hoje, a empresa americana já não comunica esses números, mas continua o seu trabalho para "ainda caber" mais.

Por ocasião do 67e edição do IDEM ou Encontro Internacional de Dispositivos Elétricosa Intel apresentou vários avanços para nos mostrar o que ela prevê para o futuro de seus processadores. No vídeo acima, Marko Radosavljevic, engenheiro sênior da Intel, entra em detalhes sobre as diferentes técnicas de empilhamento associadas a vários substratos utilizados pela empresa americana para multiplicar a densidade dentro de seus chips. Em particular, o CMOS 3D, que aumenta o empilhamento em 30 a 50% em relação às técnicas atuais, deve permitir agrupar cada vez mais transistores por milímetro quadrado.

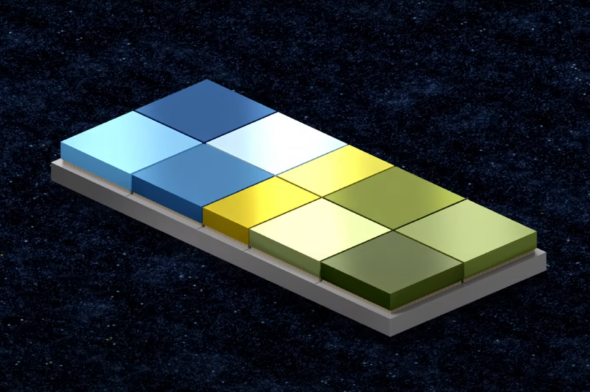

No momento, a Intel está usando o processo de gravação Intel 7 em seus processadores de geração do Alder Lake. Mais tarde, planeja mudar para Intel 4 e Intel 3. Estas mudanças serão possíveis graças ao uso de embalagens Foveros Direct em vez de Foveros. O objetivo aqui é multiplicar as interconexões a fim de, naturalmente, maximizar as trocas. A Intel já falou sobre estas melhorias, nomeadamente na conferênciaIntel Accelerated , em Julho passado.Foveros Direct utiliza ligações "cobre-cobre-cobre" que foram miniaturizadas em comparação com Foveros, de modo que o número de interligações num determinado espaço é drasticamente maior, e mais interligações significam mais trocas entre as diferentes partes dos chiplets. A Intel também aponta que o Foveros Direct também permite uma maior modularidade de design. Tudo isso se resume em três palavras:Hybrid Bonding Interconnect, ou HBI.

Finalmente, a este 67e edição do IDEM, a Intel também falou sobre a substituição dos chamados transistores FinFET (transistor de efeito de campo ou transistor de efeito de campo com barbatanas). Como a Samsung e a TSMC também podem estar a considerar, a Intel irá mudar para GAA FETs (portões em redor), uma técnica que visa modificar a estrutura do transistor para que mais canais sejam postos em prática. Neste caso, o objectivo é aumentar a precisão e, sobretudo, a estabilidade dos transístores, um assunto essencial quando o processo de gravura é refinado. A introdução de transistores GAA FET na Intel não está prevista antes de 2024 e a utilização do processo Intel 20A.